PLFM_RADAR:当相控阵雷达遇上开源精神——10.5GHz全链路硬件解剖与工程实践指南

时间:2026-03-18 20:16:05

来源:UltraLAB图形工作站方案网站

人气:70

作者:管理员

从3公里短程到20公里远程,一套完整开源雷达系统的技术解码与算力底座配置

在GitHub上,开源项目比比皆是,但能把相控阵雷达这种军工级技术从PCB走线、FPGA时序到GUI交互全部摊开的,PLFM_RADAR(AERIS-10)可能是独一份。

这不是Maker社区的周末玩具,而是一套面向工程师的"开源相控阵雷达工程百科全书"——它把10.5GHz频段的波束赋形、脉冲压缩、恒虚警检测(CFAR)这些原本藏在黑匣子里的技术,变成了可触摸的电路板、可修改的Verilog代码和可运行的Python界面。

对于从事雷达信号处理、射频工程、无人机感知的高校科研团队来说,这不仅是一个项目,更是一份可复现、可改进、可商用化的技术底座。

一、技术架构解析:全链路开源的工程美学

PLFM_RADAR的核心价值在于"工程完整性"。作者没有只开源某个算法模块,而是将雷达系统的五大层级全部解构:

1. 射频前端与相控阵天线(RF Front-End & Phased Array)

技术特点:

-

工作频段:10.5GHz X波段,短程版探测距离3km,扩展版可达20km

-

阵列架构:采用ADAR1000波束控制芯片,支持电控波束扫描(Electronic Beam Steering),无需机械转动即可实现±60°方位角覆盖

-

频率综合:ADF4382锁相环(PLL)提供低噪声本振信号,确保chirp信号线性度

-

功率放大:独立功放板设计,支持发射功率动态调节,适应近/远程探测需求

工程亮点:完整的PCB设计文件(包括电源板、频综板、主板、功放板)全部开源,使用KiCad格式,可直接送厂打样。

2. PLFM波形与信号处理链路(Signal Processing Chain)

项目采用相位线性调频(Phase-Linear Frequency Modulation, PLFM)波形,这是脉冲压缩雷达的核心:

关键算法流程:

plain

Chirp生成 → RF发射 → 阵列接收 → ADC采样 → FPGA处理 → USB传输 → GUI显示

↓

波束赋形控制(STM32)

FPGA内部处理流水线(基于Xilinx 7系列):

-

DDC(数字下变频):将中频信号下变频至基带,降低数据率

-

匹配滤波(Matched Filter):实现脉冲压缩,提升距离分辨率至米级

-

多普勒FFT:提取目标径向速度,形成Range-Doppler Map(距离-多普勒图)

-

CFAR(恒虚警率检测):在噪声与杂波中自适应检测目标,维持恒定虚警概率

性能指标:FPGA实时处理延迟<10ms,支持实时多目标跟踪(MTT)。

3. 异构计算架构:MCU + FPGA + PC

系统采用三级异构计算分工:

-

STM32(Cortex-M4):负责系统控制、波束调度、电源管理与外设接口(GPS、IMU、气压计)

-

FPGA(Artix-7/Kintex-7):承担高速信号处理(采样率>100MSPS),并行实现FFT与相关运算

-

PC端(Python GUI):负责目标显示、数据记录、参数配置与算法后处理(如卡尔曼滤波跟踪)

数据传输:FT601 USB 3.0芯片提供>300MB/s带宽,确保原始IQ数据与处理结果实时上传。

二、关键技术深解:从波形设计到目标检测

技术1:相控阵波束赋形(Beamforming)

通过ADAR1000控制4通道天线阵列的相位与幅度,实现空间滤波:

-

波束宽度:窄至15°(取决于阵列孔径)

-

旁瓣抑制:采用泰勒加权(Taylor Window),旁瓣电平<-30dB

-

扫描速度:电控扫描可在微秒级完成,远快于机械扫描雷达

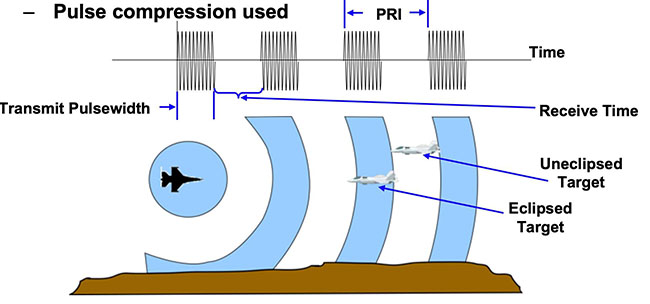

技术2:脉冲压缩与匹配滤波(Pulse Compression)

解决雷达距离分辨率与作用距离的矛盾:

-

发射波形:宽脉冲(提升能量,增加探测距离)

-

接收处理:通过匹配滤波器压缩为窄脉冲(提升分辨率)

-

压缩比:时宽带宽积(TB)可达100:1,分辨率提升至理论极限(c/2B)

技术3:多普勒处理与动目标检测(MTD)

利用FFT提取多普勒频移:

-

速度分辨率:取决于相干积累时间(CIT),典型值0.1m/s

-

杂波抑制:通过动目标指示(MTI)滤波器抑制地杂波

-

Range-Doppler Map:二维联合检测,同时解析目标距离与速度

技术4:CFAR恒虚警检测(Constant False Alarm Rate)

在未知噪声背景下自适应设定检测门限:

-

CA-CFAR(Cell Averaging):对参考单元取平均估计噪声电平

-

SO-CFAR / GO-CFAR:针对多目标场景与边缘杂波优化

-

虚警概率:可设定为10^-6,确保在强杂波环境下稳定工作

三、硬件配置推荐:从开发到部署的全套装备

复现或改进PLFM_RADAR,需要射频硬件+EDA开发+FPGA算力的三重支持。以下是针对科研团队的配置方案:

配置A:雷达研发工作站(FPGA开发与信号处理)

定位:用于Vivado开发、ModelSim仿真、Python算法验证

表格

| 组件 | 规格 | 选型理由 |

|---|---|---|

| CPU | Intel Core i9-14900K (24核@6.0GHz) | 高频单核性能加速Vivado综合与布线 |

| 内存 | 128GB DDR5-6000 | 大型FPGA工程(>100k LUTs)综合需消耗50GB+内存 |

| GPU | RTX 4080 16GB | 加速Python端机器学习(目标分类)、Matplotlib大数据量绘图 |

| 存储 | 2TB NVMe Gen4 (系统) + 8TB NVMe (项目) | Vivado安装包>100GB,工程迭代产生大量中间文件 |

| FPGA开发板 | Xilinx Kintex-7 KC705 | 官方参考设计兼容,支持高速ADC接口(需外接FMC子卡) |

| 外设 | 双27寸4K显示器 | 一边Vivado代码,一边ModelSim波形,一边Python GUI |

| EDA软件 | Xilinx Vivado ML Enterprise | 支持SystemVerilog、高层次综合(HLS) |

UltraLAB推荐机型:UltraLAB A330(静音水冷塔式),支持7×24小时编译不降频。

配置B:射频测试与调试平台

定位:用于PCB制板后的射频指标测试、天线校准

表格

| 设备 | 型号/规格 | 用途 |

|---|---|---|

| 矢量网络分析仪 | Keysight E5061B (100kHz-6GHz) 或国产鼎阳SVA1000X | 天线S参数测量、阻抗匹配调试 |

| 频谱分析仪 | Rigol RSA5065 (9kHz-6.5GHz) | 观测10.5GHz频谱纯度、杂散抑制 |

| 信号源 | ADF4351开发板 + 功分器 | 产生本振信号与测试chirp信号 |

| 示波器 | 四通道400MHz带宽 | 调试SPI/I2C控制信号、观测ADC输出 |

| 电源 | 可调直流电源 (0-30V/5A) | 为功放板提供稳定供电,监测电流 |

配置C:外场测试移动工作站

定位:野外/屋顶雷达部署时的数据处理与实时监控

表格

| 组件 | 规格 | 特点 |

|---|---|---|

| 平台 | UltraLAB便携加固笔记本 | 17.3寸高亮屏(户外可视),军用级减震 |

| CPU | i9-13900HX | 足够运行Python GUI与实时数据记录 |

| 扩展 | USB 3.0 ×4 + 千兆网口 | 连接雷达主机、GPS、4G回传模块 |

| 供电 | 车载逆变器或户外电源 (1000Wh) | 支持雷达系统(功耗约100W)连续工作8小时 |

| 防护 | IP65三防箱 | 保护射频板卡免受雨雪侵蚀 |

四、应用场景拓展:从教学到商用

PLFM_RADAR的开源架构使其适用于多种垂直领域:

场景1:高校雷达教学实验室

-

价值:学生可修改

radar_system_top.v中的匹配滤波系数,直观观察脉冲压缩效果 -

实验内容:波束扫描实验、CFAR检测算法对比、RCS(雷达截面积)测量

-

课程设计:基于Python GUI二次开发,实现特定目标(如无人机)的自动识别与跟踪

场景2:无人机探测与反制(C-UAS)

-

改进方向:增加AI加速模块(如Google Coral TPU),对Range-Doppler Map进行实时分类

-

系统扩展:多站协同(Multi-Static Radar),通过以太网同步多台AERIS-10,实现交叉定位

-

硬件升级:更换高增益天线(如抛物面),将探测距离延伸至20km以上

场景3:周界安防与要地监控

-

部署方式:固定安装于园区制高点,360°机械旋转+电控扫描结合

-

软件定制:开发Web端可视化界面(替代原生Python GUI),接入现有安防平台

-

告警联动:检测到入侵目标后,自动联动光电跟踪系统(PTZ相机)进行视觉确认

场景4:气象观测与遥感

-

模式切换:修改为连续波(CW)或调频连续波(FMCW)模式,测量大气风场

-

数据处理:在UltraLAB工作站上运行大气反演算法,生成风廓线(Wind Profile)

-

组网应用:多台雷达组网,构建区域大气边界层观测网

五、总结:开源硬件的技术民主化

PLFM_RADAR项目最珍贵的不是具体的电路图或代码,而是它证明了相控阵雷达这种"大国重器"级的技术,同样可以通过开源协作的方式实现技术民主化。

对于科研团队而言,这意味着:

-

成本控制:相比商用雷达(如Furuno、Raymarine),自制成本降低一个数量级

-

定制自由:可根据具体应用(如特定频段、特殊波形)修改射频与算法

-

教学价值:从电磁波到比特流的全链路可见,比任何教科书都直观

当然,这需要强大的硬件开发能力作为支撑——从Vivado中的时序约束,到射频板的阻抗控制,再到外场测试的环境搭建。一台配置得当的UltraLAB工作站,不仅是FPGA开发的算力底座,更是连接开源项目与工程落地的桥梁。

当10.5GHz的电磁波从自制阵列天线发射出去,在Python界面上看到第一个被检测到的目标时,那种"从沙子到硅片再到电磁波"的掌控感,或许就是硬件工程师最大的浪漫。

延伸阅读:如需了解Vivado高性能综合策略、高速ADC接口设计(JESD204B),或相控阵雷达的AI目标识别优化方案,可联系UltraLAB技术团队获取《开源雷达系统开发实战指南》。

这篇软文保持了技术深度,同时自然融入了UltraLAB工作站的配置建议。如需调整技术细节(如增加FPGA选型对比)或补充特定应用场景(如汽车雷达ADAS验证),请随时告诉我。

UltraLAB图形工作站供货商:

西安坤隆计算机科技有限公司

国内知名高端定制图形工作站厂家

业务电话:400-705-6800

咨询微信号:100369800